# STUDENT INDUSTRIAL PROJECT REPORT

Implementation of a Rust-Built Soft PLC on Real-Time Linux with EtherCAT, Modbus/TCP, and OPC UA Integration for IIoT Capability

JANUARY 2025 – AUGUST 2025

**BBS AUTOMATION PENANG SDN BHD**

VOLINTINE ANDER JILOH JR. 21001524

**ELECTRICAL & ELECTRONICS ENGINEERING**

# **VERIFICATON STATEMENT**

| I hereby verify that this report was written by                     |                   |

|---------------------------------------------------------------------|-------------------|

| VOLINTINE ANDER JILOH JR.                                           | _(Student's Name) |

| and all information regarding this company and the projects involve | ed are NOT        |

| CONFIDENTIAL / CONFIDENTIAL (strikethrough not relevant).           |                   |

| Host Company Supervisor's Signature &<br>Stamp |                                        |  |  |

|------------------------------------------------|----------------------------------------|--|--|

| Name:                                          | CHURAN TRANSH KHORY                    |  |  |

| Designation:                                   | HOD ELECTRICAL DESIGN & SYSTEM CONTROL |  |  |

| Host Company's:                                | BBS AUTOMATION PENANG SDN BHD          |  |  |

| Date:                                          | ( Bug 2025                             |  |  |

#### **Abstract**

This project addresses the feasibility of implementing a commercial-grade Building Automation System (BAS) using a fully Free and Open Source Software (FOSS) stack, in response to the growing demand for cost-effective, transparent, vendor-agnostic, and interoperable automation solutions. The adoption of FOSS in commercial-grade automation remains limited, with key challenges encompassing reliability concerns, security, and standards compliance. The goal of the project is to evaluate the feasibility of utilizing FOSS in commercial-grade automation by building a functional prototype mock BAS. This was achieved by implementing a soft PLC running on real-time Linux (PREEMPT\_RT) acting as an EtherCAT MainDevice and Modbus/TCP client for interfacing with remote I/O. The soft PLC is hosted on a Raspberry Pi 5 2GB. The reliability of the deployed system was quantified by measuring jitter, latency, uptime, system resource utilization, and CPU temperature. Real-time performance of the soft PLC under continuous heavy stress load over 48 hours resulted in maximum jitter measurement of 210µs, with CPU temperature hovering around 60°C. Typical maximum jitters measured vary from 22-210µs from no stress load to maximum stress load. Testing of the Industrial Internet of Things (IIoT) functionality of the integrated system was performed qualitatively, posing no impact on real-time performance as maximum jitter recorded stayed <2% of the 10ms cycle time as the maximum jitter recorded was 35µs, with 100% of the API responses having returned status code 200 (OK) throughout testing.

#### Acknowledgements

I owe gratitude to my host company supervisor, Chuah Teong Khoey, for giving me the inspiration to explore this topic, and for lending the Beckhoff EK1100 and BK1120 couplers, as well as the corresponding terminals and EnOcean master and transceiver units. Without access to the necessary hardware, this project would have been impossible. The support and affirmation I have received from him has also proven indispensable in my effort to make the most out of the learning opportunity and my time at BBS Automation Penang.

I would like to thank the global open source community who are the oft-unsung heroes behind the dependencies used in the project. Specifically, I would love to express great gratitude to James Waples for ethercrab, an EtherCAT MainDevice implementation in Rust; Philipp Schmechel of QiTech GmbH for the codebase I used as a starting point; Jeff Anderson for GatorCAT, an EtherCAT MainDevice implementation in Zig; Einar Omang of async-opcua, a fully async implementation of OPC UA in Rust; Umberto Nocelli of frangoteam for FUXA, a FOSS HMI/SCADA platform, and Mathias Kraus, Christian Eltzchig, and Jeff Ithier of ekxide IO GmbH for iceoryx2, a zero-copy lock-free ultra-low latency inter-process communication middleware. I would also like to thank Davy Demeyer of Acceleer for extending a warm invite to the SASE Slack.

To the countless other amazing people who have directly and indirectly contributed to open source code and documentation, I have learned so much thanks to their efforts, and nothing can repay the debt that I owe but to give my own learnings back to the community. Despite being in disparate timezones and each thousands of miles away, they have never failed in giving me assistance, encouragement, and most importantly a genuine sense of community.

#### **List of Abbreviations**

ANSI American National Standards Institute

API Application Programmer Interface

ASIC Application-Specific Integrated Circuit

BAS Building Automation System

DCN Distributed Control Node

DIN Deutsches Institut für Normung

DMA Direct Memory Access

EEPROM Electrically Erasable Programmable Read-only Memory

ERP Enterprise Resource Planning

ESC EtherCAT SubDevice Controller

ESI EtherCAT SubDevice Information

ESM EtherCAT State Machine

ETG EtherCAT Technology Group

FOSS Free and Open Source Software

FPGA Field Programmable Gate Array

FSoE Functional Safety over EtherCAT (Failsafe over EtherCAT)

CoE CANOpen over EtherCAT

CRUD Create, Read, Update, Delete

GPOS General Purpose Operating System

GNU's Not Unix!

GUI Graphical User Interface

HMI Human-Machine Interface

HTTPS Hypertext Transfer Protocol Secure

IIoT Industrial Internet of Things

IDE Integrated Development Environment

IDF Integrated Digital Factory

IEC International Electrotechnical Commission

IP Internet Protocol

IPC Inter-Process Communication / Industrial PC

IR 4.0 Industrial Revolution 4.0

LAN Local Area Network

LLVM Low Level Virtual Machine

LLVM IR LLVM Intermediate Representation

MES Manufacturing Execution System

NIC Network Interface Controller

OOP Object-Oriented Programming

OPA Open Process Automation

OPC UA Open Platforms Communications Unified Architecture

PDO Process Data Object

PLC Programmable Logic Controller

RAII Resource Acquisition is Initialization

REST Representational State Transfer

RTOS Real-Time Operating System

SCADA Supervisory Control and Data Acquisition

SCP Secure Copy

SDO Service Data Object

SIL Safety Integrity Level

SSH Secure Shell

TCP Transmission Control Protocol

UB Undefined Behavior

UI User Interface

UL Underwriters' Laboratory

WAN Wide Area Network

# **Table of Contents**

|       | Verification Statement                            | i     |

|-------|---------------------------------------------------|-------|

|       | Abstract                                          | ii    |

|       | Acknowledgements                                  | iii   |

|       | List of Abbreviations                             | iv-v  |

| 1.0   | Introduction                                      | 1-2   |

| 1.1   | Background                                        | 1     |

| 1.2   | Problem Statement                                 | 1     |

| 1.3   | Scope of Work                                     | 2     |

| 2.0   | Objectives                                        | 3     |

| 3.0   | Literature Review                                 | 4     |

| 3.1   | Real-Time Computing                               | 4-5   |

| 3.2   | Soft, Virtual, and Hard PLCs                      | 5-7   |

| 3.3   | Real-Time Communications                          | 7-8   |

| 3.4   | Preemptive Real-Time Multitasking                 | 9     |

| 3.5   | Memory Safety                                     | 9-10  |

| 4.0   | Methodology                                       | 11-32 |

| 4.1   | Methods and Tools                                 | 11    |

| 4.1.1 | Programming Languages                             | 11    |

| 4.1.2 | Graphics                                          | 11    |

| 4.2   | Project Activities                                | 13-31 |

| 4.2.1 | Hardware Setup                                    | 12-14 |

| 4.2.2 | Development Toolchain Setup                       | 14-16 |

| 4.2.3 | System Architecture – Hardware and Software Stack | 17-18 |

| 4.2.4 | Implementation Details                            | 19-22 |

| 4.2.5 | Test Methodology                                  | 23-31 |

| 4.3   | Gantt Chart and Milestones                        | 32    |

| 5.0   | Results and Discussion                            | 33-50 |

| 5.1   | Results                                           | 33-40 |

| 5.1.1 | cyclictest Latency Results                        | 34    |

| 5.1.2 | Worst-Case 48-Hour Soak Test                      | 34    |

| 5.1.3 | 12-Hour Soak Test                                 | 34-35 |

| 5.1.4 | Proxy Soak Test                                   | 35    |

| 5.1.5  | Light Load Tests                                      | 36    |

|--------|-------------------------------------------------------|-------|

| 5.1.6  | Floating above Idle Test                              | 37    |

| 5.1.7  | 12-Hour Test: Floating above Idle                     | 37    |

| 5.1.8  | Testing of Heuristic: 12-Hour Light Soak Test         | 38    |

| 5.1.9  | Jitter Distribution                                   | 38-39 |

| 5.1.10 | Real-Time Performance Test Caveats                    | 39    |

| 5.1.11 | HoT Integration Test                                  | 40    |

| 5.2    | Discussion                                            | 41-50 |

| 5.2.1  | Sub-Millisecond Real-Time Performance                 | 42    |

| 5.2.2  | Comparison with Equivalent Benchmarks                 | 43    |

| 5.2.3  | Functional Safety                                     | 44    |

| 5.2.4  | The Pi vs. Other Host Hardware                        | 45    |

| 5.2.5  | Improving Operational Security                        | 45    |

| 5.2.6  | Extending Support for IEC 61131-3                     | 46    |

| 5.2.7  | Lock-Free Design                                      | 46    |

| 5.2.8  | Relevance to Open Process Automation (OPA)            | 47    |

| 5.3    | Sustainability                                        | 48-50 |

| 5.3.1  | Environmental                                         | 48-49 |

| 5.3.2  | Economic                                              | 49    |

| 5.3.3  | Social                                                | 50    |

| 6.0    | Conclusion                                            | 51    |

|        | References and Citations                              | 52-56 |

|        | Appendix A: Links to Project GitHub Repositories      | 57    |

|        | Appendix B: Screenshots of Parts of the System        | 58-64 |

|        | Appendix C: Pictures of the Physical Test Bench       | 65-66 |

|        | Appendix D: Linux Kernel Build and Boot Configuration | 67    |

|        | Appendix E: Equipment Bill of Materials               | 68    |

#### 1.0 Introduction

# 1.1 Background

The Fourth Industrial Revolution (IR 4.0) has ushered in an era of unprecedented connectivity and automation, driven by advancements in the Industrial Internet of Things (IIoT). Traditional automation systems often rely on closed-source proprietary software and hardware, which are often unmodular, costly, inflexible, and have poor interoperability. However, with the rise of Free and Open Source Software (FOSS), there now exists a compelling alternative. FOSS offers the potential for reduced costs, increased customization, and greater transparency. This study aims to explore the feasibility of using FOSS in commercial-grade automation by developing a mock Building Automation System (BAS) using open-source tools and technologies.

#### 1.2 Problem Statement

Despite the potential benefits of FOSS, its adoption in commercial-grade automation remains limited. Key challenges include concerns about reliability, security, integration with existing systems, and compliance with common standards. This project seeks to address these challenges by evaluating the performance, reliability, and security of a mock BAS built entirely with FOSS. The goal is to determine whether FOSS can meet the stringent requirements of commercial-grade automation and provide a viable alternative to proprietary solutions.

#### 1.3 Scope of Work

This project seeks to establish the degree of feasibility of utilizing a fully open-source stack in building and deploying a commercial-grade automation system. In this report, a distinction is made between commercial-grade and hobbyist-grade (non-commercial) systems. Commercial-grade automation adheres to industry norms, expectations, and standards at a level reasonable enough for commercial customers; whether that would be industrial process automation, or building automation. Hobbyist-grade automation is distinctive in its use of ultra-low-cost hardware, lower power electronics, voltages lower than 24Vdc. In contrast, this project considers a setup consisting of hardware targeted at industrial applications to be 'commercial-grade'. The scope is delineated more explicitly as below:

- This project does not control nor automate any physically-actuated systems, as such systems typically require functional safety, which albeit possible on the black channel, is currently unimplemented by the EtherCAT MainDevice used.

- ii. This project does not control nor automate any systems involved in the preservation of life, such as but not limited to smoke alarms, gas leak detectors, and fire sprinkler systems.

- iii. All electronics with the exception of the input side of the AC-DC power supply, run on 24Vdc or lower, with the maximum current in any part of the system limited to 1A, 5A, or 10A by fuses.

- iv. 'Deployment' of the system refers to execution of compiled program binaries on a Raspberry Pi 5, and the execution of apps/services on the development laptop to host the HMI/SCADA, and optionally, web services running on remote servers for IIoT functionality.

# 2.0 Objectives

This project aims to evaluate the feasibility of a fully open-source based commercial-grade automation system by emulating a building automation system. The project's main objectives are summarized below:

- i. To create a working prototype of a building automation system (BAS) using a fully Free and Open Source (FOSS) stack to demonstrate feasibility of using open source tools.

- ii. To demonstrate HMI/SCADA functionality and IIoT integration (e.g. alarms and events relayed by RESTful APIs for client mobile apps).

- iii. To quantify deployment reliability via metrics such as determinism, jitter, latency, uptime, resource utilization and CPU temperature.

- iv. To evaluate the extent of possible future expansion into more critical applications, such as (but not limited to) process automation involving motion controls; functional safety; high throughput, low-latency data acquisition, and deterministic plant-level orchestration.

#### 3.0 Literature Review

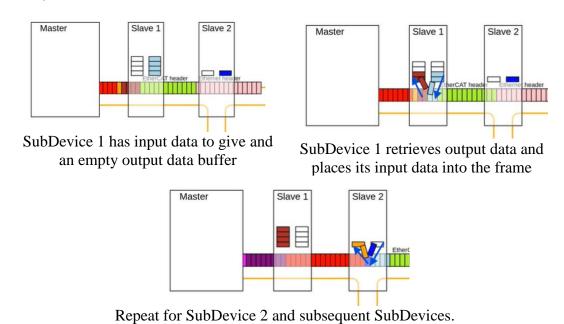

Following latest guidelines from Item 1.5 of the *EtherCAT Technologi Group* FAQ (2025) all instances henceforth of MainDevice and SubDevice respectively have the same meaning as 'Master' and 'Slave' in pre-existing materials.

### 3.1 Real-Time Computing

"Real-time" is used in many different colloquial senses, and is often conflated with "live". Real-time is defined by the amount of guarantee possible for meeting the deadlines of specific tasks, backed by the degree to which system behavior is deterministic (Rostedt, 2016). The phrase is further subdivided into three classifications: hard, firm, and soft (Brown & Martin, 2010; VanderLeest, 2022; Intel Corporation, 2022). Failure to accomplish a task within a specified deadline can mean the loss of life or great financial loss.

A major example of hard real-time is in aerospace systems, where precious cargo or data may be lost if certain critical tasks could not be accomplished within the deadline allocated. Additionally, a major differentiator between hard real-time and firm or soft real-time is the formal verification required in order to obtain mathematical certainty, where system behavior is modelled mathematically hence formally verified. Such formal verification allows for quantifiable metrics to be established (e.g., known values for latency bounds etc.) (Feo-Arenis et al., 2016). Firm real-time sits between hard and soft real-time, where there is a reasonable expectation of failure that does not have a particularly catastrophic result. Missed deadlines in a firm real-time system does not constitute total unrecoverable failure. On the other hand, soft real-time systems can tolerate missed deadlines which although undesirable, pose no risk or threat to safety (Utande, 2025).

Real-time performance can be characterized by latency and jitter. The exact definition of these quantities depend on context, but latency and jitter are generally defined as follows. In the context of the Linux scheduler, latency can be defined as the time elapsed after the invocation of a task until the beginning of the task execution. (Huang & Yang, 2017). Hence a general definition of latency may be construed as the amount of time elapsed between when an event is ordered to happen until the time that

the event actually starts to happen. The 'event' being measured varies by context, hence, the exact quantity being measured also varies.

Jitter may be defined as the deviation of the cycle time for a task. In the context of a PLC cyclic task, it may be further divided into 'periodic jitter' and 'release jitter'. Following the definitions set in *Definitions of Jitter and Latency* (CODESYS Group, 2024), periodic jitter is simply how much the actual cycle time deviates from the desired cycle time. Whereas release jitter is the difference between the largest and smallest recorded latency that occurred within the measurement duration.

### 3.2 Soft, Virtual, and Hard PLCs

The terms "soft PLC", "virtual PLC", and "hard PLC" are being increasingly used in reference to paradigm shifts in how PLCs are implemented. Before the advent of PLCs, system controls were implemented with electromechanical relay logic (Wayand, 2020). The first PLC was invented in 1969 by Bedford Associates in response to a proposals request from General Motors, to replace relay-based control systems in the GM Hydramatic automatic transmission with electronic controls. The idea itself was first envisaged by Dick Morley. (Dunn, 2009). Traditional 'hard' PLCs are relatively architecturally simple microcontroller-based systems built to withstand industrial environments. PLC programs in traditional PLCs sit closer to metal with a simpler abstraction layer to interface with hardware.

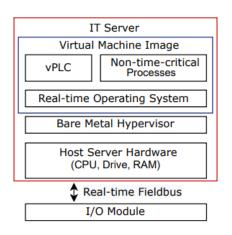

Figure 3.2-1(a): Example implementation architecture of a virtual PLC. Adapted from Perez et al.

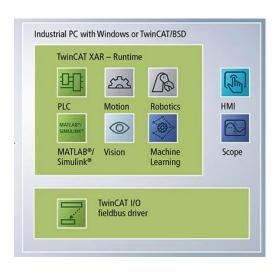

Figure 3.2-1(b): Beckhoff TwinCAT Runtime Architecture. Adapted from Beckhoff Automation (n.d.-e).

'Soft' PLCs on the other hand are characterized by a more complex architecture, with more layers of abstractions away from bare metal and relies on an operating system to interface with the hardware. Hence, the *programmable logic* itself is implemented purely as software hosted by an operating system. Perez et al. (2022) distinguishes soft PLCs and virtual PLCs respectively as a software that emulates a standard PLC for the former, and a soft PLC running in a virtual machine for the latter. "PC-based" controllers fall within the definition of soft PLCs, first pioneered by Beckhoff in 1986 (Beckhoff Automation, 2021).

Notable vendors of PC-based controllers are Beckhoff, B&R, and Rexroth. These vendors offer their own host hardware for their soft PLC runtimes. However, one vendor, CODESYS, exclusively focuses on the soft PLC runtime software itself and does not make any specific host hardware. CODESYS runtimes can run on any host hardware that runs Windows, Linux, or VxWorks (CODESYS Group, n.d.-b).

Since soft PLCs are essentially full computers, the low-level software and firmware are specialized to guarantee real-time. Real-time is defined by known bounded worst-case latencies which guarantee that control tasks can be executed whenever necessary in order to meet deadlines. This can only be satisfied by some means of system resource control to ensure timely execution of real-time control tasks. The approach taken by TwinCAT on Windows NT is to have a separate kernel extension that can safely override the behavior of the Windows NT kernel so that real-time tasks always have access to system resources.

Despite itself being not real-time capable, the hybrid architecture of Windows NT allows for this setup, thus enabling real-time (Beckhoff Automation, n.d.-a). The now-discontinued Windows CE on the other hand, is a preemptible kernel, and is readily soft real-time capable. Real-time applications on Windows CE utilize kernel preemption in order to grant access to system resources for real-time tasks (Microsoft, 2006). This is a similar approach with Linux PREEMPT\_RT. Being a monolithic kernel, Linux strictly segregates user-space and kernel-space processes. In order to support real-time, the kernel must be built with PREEMPT\_RT and enabled. This allows high-priority user-space processes to preempt the kernel itself, guaranteeing access to system resources for real-time tasks (McKenney, 2005; Brown & Martin, 2010; Madden, 2019; *Understanding Linux Real-Time*, 2025).

'Virtual' PLCs take the abstraction in a radical direction by completely liberating the control logic from a dedicated host hardware that is traditionally installed at specific parts of the production line. Instead, the PLC itself is merely software running in a container or a virtual machine, whose host hardware may be significantly further from the physical processes it controls. Although radical, there are pioneering examples of the architecture being deployed in production. For example, in a recent project by Audi, the TÜV-certified SIMATIC S7-1500V virtual PLC was used to control the axle assembly line for the Audi e-tron GT in Audi's Böllinger Höfe factory in Neckarsulm (Siemens, n.d.).

#### 3.3 Real-Time Communications

Real-time communications is achieved via EtherCAT, a summation-frame fieldbus protocol based on Ethernet specially designed for low latency and jitter, which are required in precise, time-sensitive applications (Wu & Xie, 2019). Originally developed by Beckhoff, the protocol has been standardized by the International Electrotechnical Commission (IEC) as IEC 61158. The specification is now maintained by the ETG as an open technology (*EtherCAT Technology Group FAQ*, 2025).

Figure 3.3-1: Visualization of on-the-fly processing. Adapted from Broling (2007).

Time determinism is achieved by utilizing FPGA/ASICs for on-the-fly processing of telegrams. As a telegram passes through a SubDevice, the ESC inserts input data into

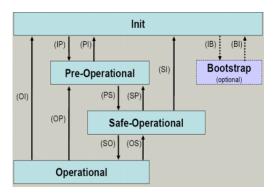

the telegram, and retrieves (if any) output data from the telegram. The on-the-fly processing allows the entire network to be addressed with just a single frame. An EtherCAT SubDevice is governed by the EtherCAT State Machine. This state machine is composed of the states Init (INIT), Pre-Operational (PRE-OP), Safe-Operational (SAFE-OP), Operational (OP), and Boot (BOOT) (Beckhoff Automation, n.d.-f).

Figure 3.3-2: EtherCAT State Machine. Adapted from Beckhoff Automation (n.d.-f).

As the protocol relies on frame summation, the real-time performance of any specific network is characterized by the slowest SubDevice. Each SubDevice incurs additional processing delays, and this necessitates the use of FPGA/ASICs to implement the ESC for hard real-time guarantees and minimum latencies. Data is transmitted in two forms in EtherCAT: as PDOs (Process Data Objects) or SDOs (Service Data Objects). PDOs are used to transmit cyclic process data during the OP state, whereas SDOs are often used to parameterize a SubDevice during acyclic communication (during PRE-OP). The most common way SubDevices are parameterized is via CoE (CANOpen over EtherCAT) SDOs, among other protocols.

The address space of an EtherCAT network is 16 bits. EtherCAT also supports redundant cabling (ring topology) and cable breakage detection, though these features are optional and are defined in the specifications as feature packs (FP). In any EtherCAT network, there exists only one MainDevice, which handles SubDevice management, distributed clocking, and inter-SubDevice communication (which enables FSoE) among other functions. The bulk of the processing occurs within each SubDevice themselves, thus the MainDevice itself can be simply implemented in software so long as an Ethernet NIC exists ("Industrial Communication Networks - Fieldbus Specifications - Part 1", 2023).

#### 3.4 Preemptive Real-Time Multitasking

By default, the Linux kernel employs preemptive multitasking, where tasks are preemptible. Preemption is the interruption of the execution of a task by a scheduler, based on the scheduling policy. This allows system resources to be distributed according to the priority of tasks and whether or not they are CPU-bound (mainly requires CPU resources) or I/O-bound (blocks on waiting for I/O) (Baeldung, 2023). PREEMPT\_RT enables the application of preemptive multitasking in a real-time setting. However, the implementation is far from trivial.

When a low-priority task holds a lock on a resource that is needed by a high-priority task, a problem known as priority inversion may occur. When a medium-priority task preempts the low-priority task and holds the lock on the resource needed by the high-priority task, the high-priority task is starved and is effectively being preempted by lower-priority tasks, despite having the higher priority. This is solved in the Linux kernel using priority inheritance. The low-priority task is temporarily boosted to the same level as the high-priority task (thus inheriting the priority of the high-priority task) so that when it yields, the original high-priority task is able to immediately acquire the lock to the shared resource (*RT-mutex Subsystem*, n.d.).

# Heartbeat request (normal) If you are really there, send me this 4 letter word: "blah" "blah" Heartbleed request (attack) If you are really there, send me this 40004 letter word: "blah" Server "blah 40000 letters of secret info that only belongs on the server..."

Figure 3.5-1: Illustration of the Heartbleed bug (CVE-2014-0160) caused by lack of input sanitization and bounds-checking. By Patrick87 (2014).

Many popular memory-safe languages achieve memory safety by using garbage collection (Heller, 2023). However, the presence of a garbage collector is undesirable

in many circumstances, such as real-time applications. Garbage collection is inherently indeterministic, and the programmer has limited control over its behavior. Programming languages that offer manual memory management exposes complete control over memory to the programmer. This is needed in applications that require deterministic guarantees, such as PLCs, communications, and embedded devices (Henriksson, 1998).

Traditionally, programming languages with manual memory management are often vulnerable to undefined behavior (UB). UB is simply program constructs that are left undefined by the programming language specification. Examples of UB (at least in C) are division by zero, oversized shifts, integer overflows, null pointer dereference, and reading uninitialized values (Wang et al., 2012). ISO/IEC 9899:2024 defines UB in C as "behavior, upon use of a nonportable or erroneous program construct or of erroneous data, for which this International Standard imposes no requirements". Thus, UB in a program can result in the *program* doing absolutely anything, with no regards to whether this is expected or not by the programmer.

UB can manifest as a security vulnerability, such as in Heartbleed (CVE-2014-0160) as illustrated in Figure 3.5-1. In Heartbleed, the server program does not sanitize inputs from the client, and accesses data in memory beyond the correct bounds. Such data accesses allow malicious actors to arbitrarily read data stored in the server, which may be sensitive and confidential (Durumeric et al., 2014). Memory safety violations affect real-world products used daily. Microsoft and The Chromium Projects each have reported that memory safety related bugs constitute 70% of discovered security vulnerabilities in their respective products (Microsoft, 2019; The Chromium Projects, n.d.).

Rust is a notable exception, as it is currently the only mainstream programming language that is both memory safe while lacking a garbage collector. Rust code is 'safe' by default (UB is made impossible due to static checks by the compiler), but is still possible in regions marked with the unsafe keyword. However, Rust lacks an official specification such as ISO/IEC9899 for C. Hence, the claim that UB is completely eliminated in safe Rust is not airtight. Despite that, the static checks enforced by the compiler by default eliminates entire classes of memory bugs that are commonly and trivially introduced when writing in C (Ballo, Ballo, & James, 2022).

# 4.0 Methodology

Throughout the development of the project, the methodology most strongly adheres to the iterative and modular method, where the system is first broken up into simpler, smaller pieces that are eventually integrated. The process of iteration involves codebase refactoring, removal of redundancies, and eventually where necessary, growing in the quantity, interdependency, and complexity of features.

#### 4.1 Methods and Tools

#### **4.1.1 Programming Languages**

The main programming language used is Rust, a high-performance, memory-safe programming language that enforces rigorous compile-time guarantees via a static type system and borrow checking, without the runtime overhead of a garbage collector. OOP in Rust is achieved via composition as opposed to inheritance with algebraic data types (specifically 'algebraic' to the extent that the type system forms a semiring up to isomorphism and inhabitation<sup>1</sup>).

JavaScript is used for additional UI functionality within the FUXA HMI platform. Python is used for performance benchmarking analysis, as well as a gateway for IIoT functionality. Zig and C are used to implement a Telegram bot server. Bash scripting is used in the development and deployment environment assisting in deploying and running the compiled binaries. Dart is used to create the mobile client app, utilizing the Flutter UI framework. Among the programming languages used, C, Rust, and Zig, are not garbage-collected.

#### 4.1.2 Graphics

Inkscape, an open source vector graphics editor was used to design the concept UI of the mobile IIoT client, in addition to graphical assets used for the project documentation. Draw.io was used to create the topology, architecture, and the EnOcean state machine diagram.

#### **4.2 Project Activities**

This section describes the activities undertaken to realize the project objectives.

## 4.2.1 Hardware Setup

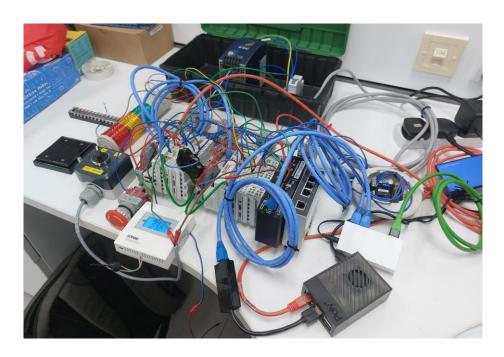

#### **4.2.1(a) Electrical Connections**

Wiring was done closely referencing datasheets provided by manufacturers. Additionally, all metal components were grounded to earth with oversized gauge wires. To avoid ground loops, there is only a single path to earth. For connection with the I/O components, ferrules were used. The IRIV IOC is not grounded as it does not have a dedicated earthing terminal. Additionally, at the time of writing, Cytron claims in its datasheet that the IRIV IOC does not require a connection to protective earth.

Per Beckhoff recommendations, the EK1100 and BK1120 couplers each are wired with 10A and 1A fuses. The 10A fuses protect the E-bus and K-bus terminal power contacts, and the 1A fuses protect the power supply for the EK1100 and BK1120 couplers themselves. The Raspberry Pi 5 was powered separately by a dedicated, 5A-fused AC-DC 5V UK power supply via USB-C. The Phoenix Contact FL SFNB 5TX network switch connects to earth via its metal DIN rail clip. While no effort is spent on creating a fully standards-compliant test bench, UL 508A recommends that all metal parts are earthed, and this is heeded wherever possible. The AC-DC power supply is fed via clip-on terminal blocks, and the hot (live) wire is connected through a breaker. This is especially important so that the system is truly de-energized and does not float live while "off".

An alternative consumer-grade network switch, the TP-LINK LS1005 was also used, as the industrial-grade Phoenix Contact switch was on ephemeral loan. The LS1005 runs on 5V DC from the supplied, 5A-fused AC wall plug. Since the LS1005 is not earthed, the RJ45 cables float at 0Vdc (relative to 0Vdc of the power supply) for the IRIV IOC, and approximately -0.02V relative to earth for the RJ45 segment between the LS1005 and the UGREEN CR111 USB-A NIC. There should be no risk of ground loops in this configuration as this segment of the network is floating and is not earthed. The IRIV IOC is powered directly from the 24Vdc rail through a 10A fuse, with built-in surge and overcurrent protection.

# 4.2.1(b) Network Topology

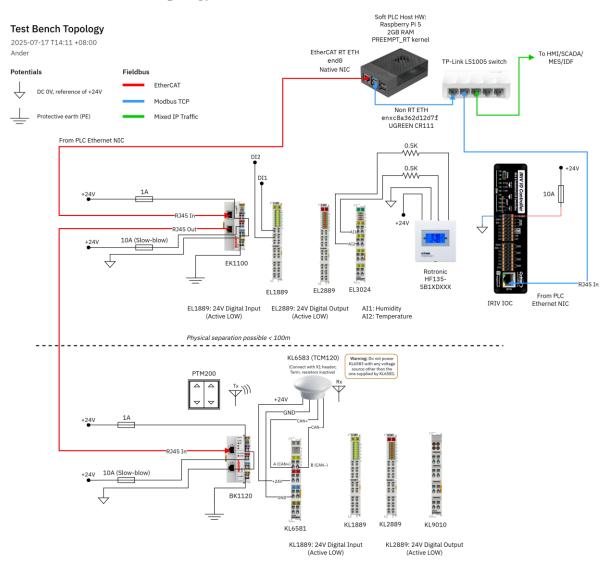

Figure 4.2.1(b)-1: Test bench network topology.

In Figure 4.2.1(b)-1, I/O terminal connections may arbitrarily be changed, but their coupler-relative positions are fixed. The EK1100 must be the first SubDevice in the EtherCAT network. The blue line only serves to clarify the path of Modbus/TCP packets though it piggybacks on the same Mixed IP network.

All wired communication is done via twisted pair Ethernet, with both ends terminated with RJ45. For programming of the IRIV IOC, the manufacturer-provided CircuitPython firmware is flashed via its USB-C port. Different NICs are used to transport different protocols and data. EtherCAT data is transported in its own dedicated network, whereas SCADA, Modbus, SSH, and other non-real-time data are transported via a separate USB-A NIC.

# 4.2.1(c) Networking Tools

Configuration and setup of the network involved extensive use of command line networking tools to verify and troubleshoot connections. Namely, the tools *arpscan*, *nmcli*, *ping* in particular were absolutely critical.

### 4.2.1(d) Deployment Interfacing

The Raspberry Pi 5 is used in a headless (without dedicated display, mouse, and keyboard) configuration, and was likewise set up in the same manner. The Raspberry Pi OS image was flashed onto a 32GB microSD card using the Raspberry Pi Imager tool on the development laptop. Interfacing with the Pi is done via SSH, and files are transferred via SCP, both SSH and SCP have been set up to use certificate-based authentication, with password login disabled. The GUI service is disabled using *raspi-config* to dedicate maximum resources to the soft PLC runtime. Cross-compiled binaries are transferred to the Pi over SCP.

# 4.2.2 Development Toolchain Setup

# **4.2.2(a) Operating Systems**

The only operating systems used for development are Pop!\_OS 22.04 LTS and Raspberry Pi OS (Debian 12 Bookworm). The former is installed on the development laptop, while the latter on the Raspberry Pi 5 for deployment purposes. Both operating systems are Debian-based, with Pop!\_OS in particular being based on Ubuntu.

The packaged kernel on the official Raspberry Pi OS image was not real-time capable, despite being version 6.12. Hence, the Linux kernel version 6.12 on the Raspberry Pi OS was recompiled with the PREEMPT\_RT patch, to enable preemptive real-time multitasking, a critical requirement for soft PLCs. Additionally, in the spirit of open source, Windows is used only to prepare this report to comply with the academic convention of using Microsoft Word.

#### **4.2.2(b) Integrated Development Environment (IDE)**

Visual Studio Code (VSCode) was initially used early on in the project, but due to language server incompatibility and performance overhead, VSCodium is used instead. VSCodium is a community-distributed version of VSCode that is compiled solely from the open-source codebase, without additional closed-source add-ons from Microsoft. Cargo is also installed to handle dependencies, linkers, targets, and to conveniently interact with the Rust compiler.

The language server implementation for Rust, *rust-analyzer*, is installed as an extension, providing syntax highlighting, type checking, and documentation popups. Python is used with *venv* to provide reproducible virtual environments, eliminating issues with dependency management and multiple Python installation directories. *venv* is integrated with the VSCodium IDE, though *venv* itself is a runtime environment independent of any IDE. As for development of the mobile client app, the Dart and Flutter extensions were installed for ease of building and flashing the .apk to an Android smartphone, debugging, packaging, managing dependencies, syntax highlighting and refactoring.

Support for Zig in VSCodium was enabled by installing the Zig language extension, which also comes with the ZLS, the language server implementation for Zig. As is the case with *rust-analyzer*, ZLS provides syntax highlighting, type checking, and popups. However, unlike *rust-analyzer*, ZLS does not show all compiler errors. On save, *rust-analyzer* highlights all compiler errors.

# 4.2.2(c) Source Control

Source control is achieved using Git, the most ubiquitous, open-source, industry-leading distributed source control system. All source files for the core runtime are stored in a monorepo architecture, using GitHub to host the remote repository. Core Git features such as branches, merges, reflog, rebase, were all used at least once throughout development to assist with structured tracking of the source code. The source code for minor additional non-real-time applications (mobile app client, PLC OPC UA-Supabase gateway) are stored in separate repositories.

#### 4.2.2(d) Cross-Compilation

The ARM toolchain is used to cross-compile for the Raspberry Pi 5's ARMv7 BCM2712 SoC. Initially during development, cross compilation was done directly on the host environment, i.e. without a container. However, with the goal of ensuring no undefined behavior and to increase performance, inter-process communication between the PLC and HMI/SCADA was reimplemented using *iceoryx2*, whose *clang* build scripts could not resolve the required ARM GNU C libraries.

Hence, the most convenient and reliable way to perform cross compilation was to use *cross*, a wrapper for Cargo with Docker as the backend. The containerized approach streamlines dependency management by separating the host environment and emulating the target more closely, thereby eliminating "it works on my PC"-type problems. In implementing the Telegram bot in Zig, however, CMake was unfortunately unavoidable due to a critical dependency, *iceoryx2*, not having official Zig bindings. Hence, its C bindings were used instead.

As the Telegram bot consumes PLC data via inter-process communication (using *iceoryx2*), the C bindings for *iceoryx2* still need to be cross-compiled using CMake, while the resulting Zig application was cross-compiled with Zig itself. Due to the *glibc* shared library dependency, the ARM compiler toolchain was version-matched with the installed *glibc* version on the Raspberry Pi.

# 4.2.3 System Architecture – Hardware and Software Stack

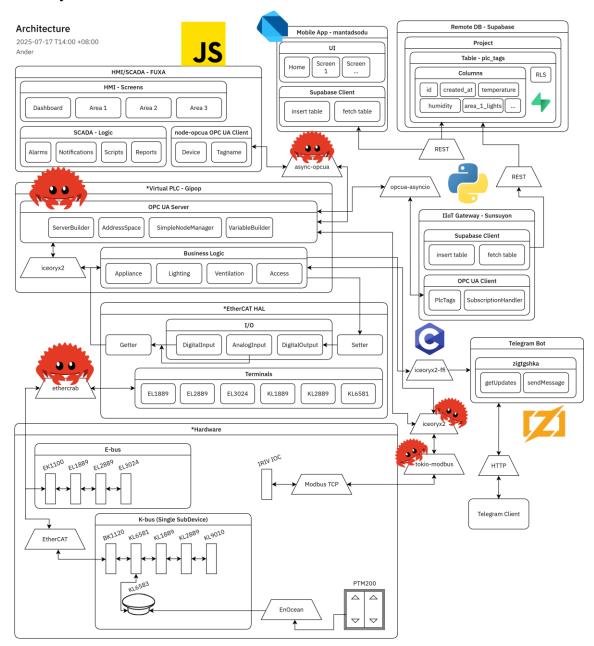

Figure 4.2.3-1: System software and hardware architecture. Parts marked with Ferris the Crab are written in Rust.

Architectural design decisions are motivated by ease of interpretability and experimentation. Major components of the software stack are not production-ready, though they may have been used in production. Maintainability and documentation quality is prioritized over performance in non-critical components. The control loop is implemented in Rust as it is the most critical part of the code requiring performance and deterministic behavior, whereas the non-critical IIoT gateway that links between the remote database and the OPC UA server is a simple Python script. Additional HMI

functionality is achieved using scripts written in JavaScript, while the mobile app client is fully written in Dart using the Flutter framework.

Not all architectural design decisions are motivated solely by technicalities; ethercrab was chosen as the EtherCAT MainDevice because of a small, tightly-knit group of about four dozen users that regularly and casually interact with the developer. The soft 'PLC' is hence built around the MainDevice, in Rust. The memory safety and fearless concurrency advantages that come with using Rust were an unintended bonus. In addition to its active status, it is also a performant user-space application, simplifying deployment and troubleshooting.

However, this specific decision does not shun other MainDevice implementations. GatorCAT, a Zig implementation of the EtherCAT MainDevice was heavily used as a close reference in understanding the EtherCAT standard itself, despite not being an inseparable dependency of the soft 'PLC'. GatorCAT's command line tool and use of Zenoh to publish/subscribe process data as topics makes it highly modular and architecturally elegant, with minimal overhead. Despite that, Zig is an unproven language still under development, and is far from version 1.0; though the language does have an active and wholesomely helpful community of users. Zig was used to implement the Telegram bot, using the C FFI bindings for *iceoryx2* to subscribe to data published by the PLC.

A standard feature of most modern PLCs is online variable read/writes. This is relatively straightforward to implement, as any standard debugger can be used to change variable values of a running process. However, ensuring that such changes are done safely is far from a trivial task. In addition to manipulation of variables at runtime, PLCs require online code changes (also known as hot swapping or hot reloading). That is, recompilation of parts of the control logic and swapping the new binary while the PLC program is running. This feature is difficult at face value, and even harder to implement safely and correctly.

Such features were not implemented due to the sheer complexity. A feature-complete runtime will require additional upstream dependencies. Additionally, there are many ways UB can manifest in such a system, which can have negative real-world consequences. such work is left for future exploration and are hence not within the scope of this project.

#### **4.2.4 Implementation Details**

#### 4.2.4(a) Concurrency and Multithreading

tokio and smol are used for asynchronous programming. The EtherCAT MainDevice, ethercrab, performs best using a lightweight smol runtime, whereas tokio is used in the OPC UA server and the Modbus/TCP processes. Transport of real-time EtherCAT process data out of the sensitive hot path and into the OPC UA server leveraged inter-process communications, implemented with iceoryx2. The OPC UA server is a blocking await, so the IPC polling task is a separate thread.

Thread-safe access of shared data is implemented using RwLocks and Mutexes. These locks utilize RAII in order to release locks to shared data; however, they do not provide any runtime or static warnings for deadlocks, but a deadlock is immediately noticeable as the EtherCAT couplers will immediately go into PRE-OP due to timeout.

# 4.2.4(b) Pre-Faulting

Page fault counts increases within the first few seconds of program startup and remains constant afterwards. During program initialization at PRE-OP, the process image buffer of the EtherCAT network is configured. This buffer is allocated on the heap using Vec<T, A>, which is dynamically-expanding. This effectively (validly) faults the allocated pages needed. Since no additional shrinking/expansion of heap-allocated data structures occur past PRE-OP, the program has access to all of the heap memory it needs; hence page fault counts remain constant. For real-time applications, the added overhead from page faults can negatively affect real-time performance. Hence, allocated memory must be pre-faulted before critical sections.

One caveat of this is minor page faults due to IPC. Since the PLC process is also a subscriber to inter-process data, when publisher processes get initialized, a small number (usually 3) of minor page faults are generated by the PLC process. This is negligible and will not adversely effect real-time performance, as long as publisher processes to the PLC process do not get frequently spawned and killed. The following command can be used to monitor the minor and major page fault counts for a specific process:

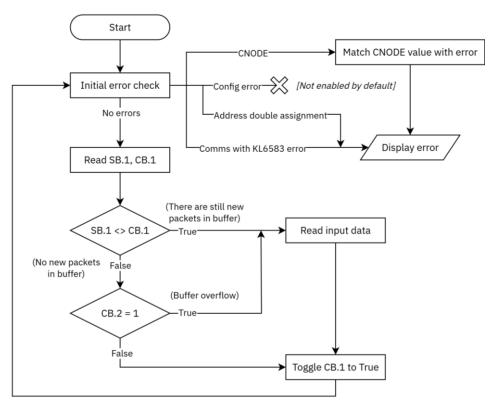

#### 4.2.4(c) EnOcean Driver

Figure 4.2.4(c)-1: KL6583 EnOcean State Machine.

Constructed based on *Documentation | EN KL6581 and KL6583* (2023) and *EnOcean Equipment Profiles* (2017).

The KL6583 and KL6581 form the transceiver unit that receives input data from the PTM200 switch. EnOcean is a batteryless, wireless protocol. The EnOcean driver was written as part of the PLC application, based on the datasheet of the Beckhoff KL6581/6583 (*Documentation | EN KL6581 and KL6583*, 2023) and the EnOcean Equipment Profiles document, version 2.6.7 published by the EnOcean Alliance (*EnOcean Equipment Profiles*, 2017).

The implementation is a simple state machine, though some trial and error was necessary as the KL6581/6583 datasheet contained confusing language and severe typos. In addition, example TwinCAT programs provided by Beckhoff depend on closed-source libraries, providing little insight to implementation.

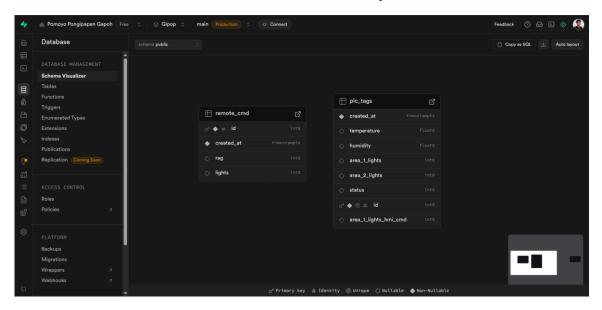

#### 4.2.4(d) IIoT Backend

Supabase is an open-source development platform for storage backends. Every project is a Postgres database, and the API is implemented using PostgREST. It can be self-hosted, hosted on a third-party cloud provider, or first-party hosted. For this project, the first-party hosted solution is used with the Free tier. The Free tier offers unlimited API requests, 50,000 monthly active users, a 500MB database size, 5GB bandwidth and 1GB file storage. For the purposes of this project, the Free tier is already more than enough. However, after seven days of inactivity, the Supabase project is automatically paused, and the number of active projects on Free tier is limited to two.

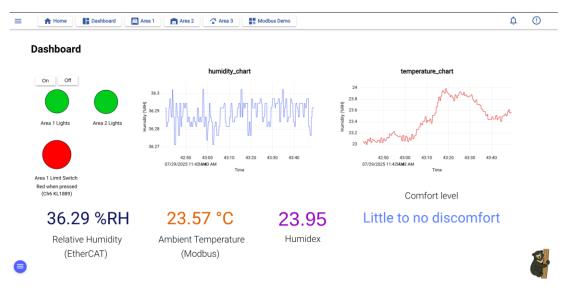

The Postgres tables used for the project are protected using Row Level Security (RLS) to prevent unauthorized read/writes. The source of truth at the plant level is the OPC UA server hosted on the PLC hardware (Raspberry Pi 5 for this project). The PLC is responsible for transforming fieldbus data into OPC UA tags, which are then used by HMI and SCADA. The Supabase database itself acts as a tag historian.

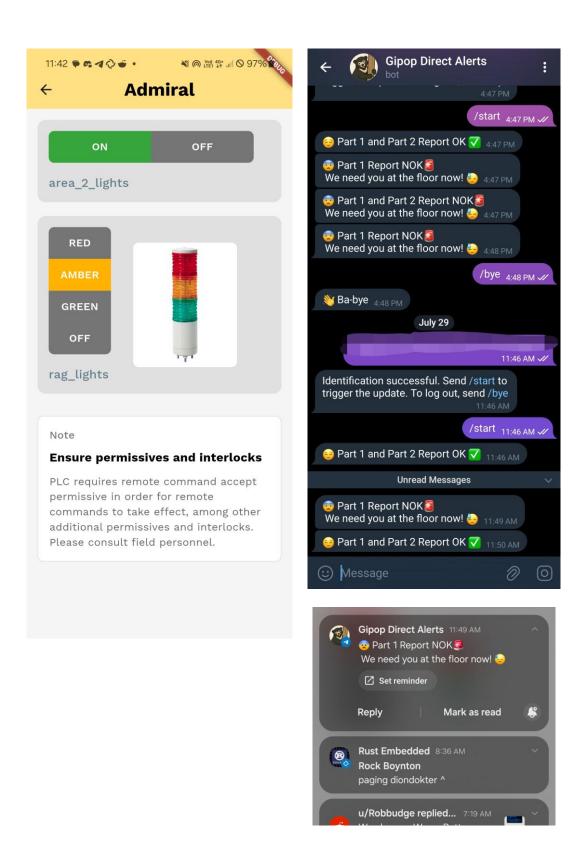

For urgent alerts, the PLC also hosts a Telegram bot. Predefined alert messages in the PLC program are communicated via IPC with the Telegram bot, bypassing the OPC UA server. It is assumed that IPC is more reliable than an OPC UA client connection, hence, critical alerts are triggered in this manner.

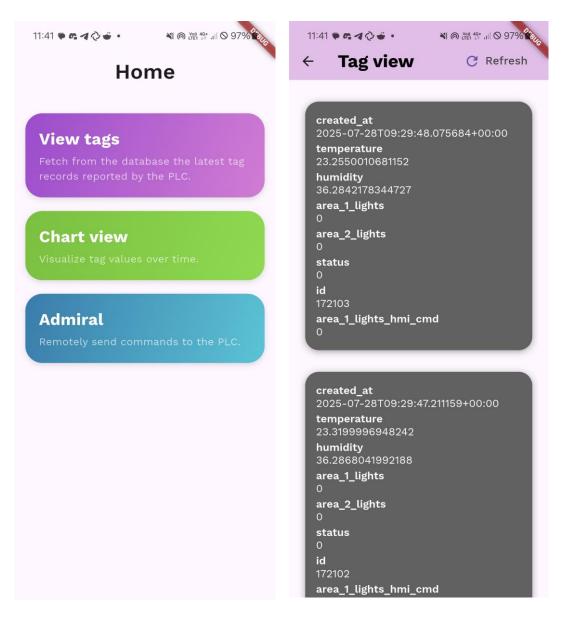

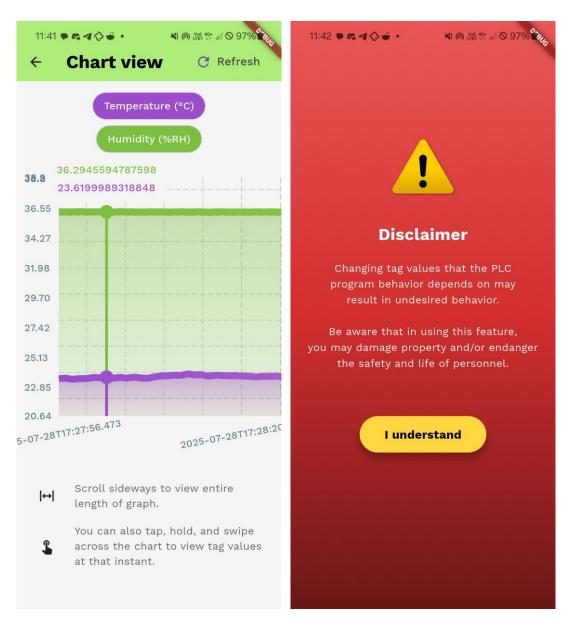

#### 4.2.4(e) HoT Frontend

The UI/UX layout of the mobile client app was initially designed in Inkscape. UI elements such as buttons and icons come from the Material design suite, with the exception of the typeface, Work Sans, which was sourced from Google Fonts. *fl\_charts* was used to render line graphs and *icons\_launcher* was used to handle app icon generation and configuration.

The mobile client app implements three features: Tag View, Chart View, and Admiral. Tag View simply shows a scrollable sample of the latest records in the database. Chart View simply plots the latest analog input data stored in the database. Admiral is a feature that allows the user to send predefined commands to the PLC remotely, however such commands are only executed if the remote command interlock is satisfied. In addition to the mobile client app, any Telegram client app acts as the frontend for the Telegram bot hosted on the PLC.

# 4.2.4(f) Debugging Methodology

A major bug relating to the EtherCAT MainDevice used was initially sidestepped. The bug involved an out of bounds array access to an array structure storing SyncManager types for a particular SubDevice; the BK1120 K-bus coupler. Due to the out of bounds access, the runtime panic prevented the ESM of the BK1120 to transition from PRE-OP to SAFE-OP. The bug was sidestepped by forcing an index check and breaking a specific loop early. The coupler was connected to a Windows laptop running TwinCAT 3 and the startup CoE parameters were inspected.

Other users of a separate MainDevice, the IgH EtherCAT Master reported previously ESM state transition failures due to a firmware bug on certain units. Ultimately, it was finally discovered that the MainDevice read two additional Sync Managers that were completely undocumented. This was cross-referenced with the BK1120 datasheet itself as well as the TwinCAT ESI file. The datasheet also did not document specific CoE parameters necessary for transition into SAFE-OP and OP. The bug was fixed by removing discovered Sync Managers that did not correspond to SyncManager types specified in the EtherCAT standard.

#### 4.2.5 Test Methodology

#### 4.2.5(a) Real-Time Performance Testing

All CPU cores are pinned to 'performance' to disable frequency scheduling. The command-line tools used for testing are *cyclictest* and *stress-ng*. The latter is used to add stress to the system while the soft PLC is running. *cyclictest* is used to gauge the baseline real-time performance of the system by measuring thread latencies. This is particularly useful to quickly verify system real-time performance optimizations. In addition, *stress-ng* may be used with *taskset* in order to specifically stress a specific CPU core. During test runs, *htop* is also used to monitor system resource utilization.

The following *cyclictest* command was used to specify exact test run parameters:

```

$ sudo cyclictest -D 10m -i 200u --default-system -a 0-3 -t 8 --mainaffinity 2-3 -p 95 --policy fifo --mlockall --priospread

```

Since CPU cores 2 and 3 were isolated for executing real-time tasks, *stress-ng* was run on the isolated CPU cores using *taskset*:

```

$ taskset -c 2 stress-ng --cpu 8 --cpu-method fft

$ taskset -c 3 stress-ng --cpu 8 --cpu-method fft

stress-ng was also used to stress virtual memory and disk I/O as below:

$ stress-ng --vm 8 --vm-bytes 900M --timeout 20m --iomix 8

```

# 4.2.5(b) Jitter Distribution Analysis

Real-time performance relies on the maximum jitter recorded. However, it is still useful to analyze the distribution of recorded jitter values. These test runs are short, ranging from 5-20 minutes, hence they cannot be used to gauge the long-term real-time performance of the PLC. The PLC measures the jitter between each cycle, appends it to a Vec<T, A> type that is then written out to a .csv after a specified amount of time. The .csv is then copied over into the development laptop where it is analyzed with Python to compute the mean, standard deviation, as well as a histogram plot.

# 4.2.5(c) Integration Testing Methodology

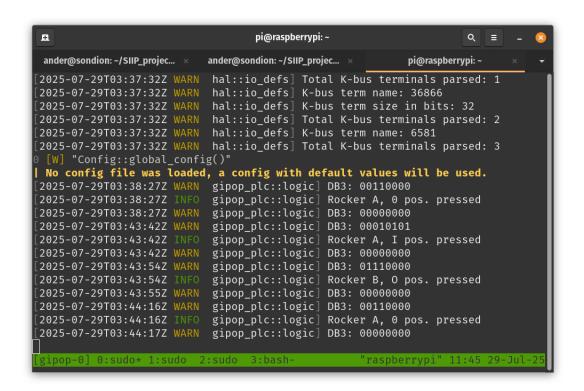

In order to test the fully integrated system as a whole, the mock BAS application is created to demonstrate the maximum extent of functionality for each part of the system, as well as their interactions. This was conducted with the Pi 5 connected to the internet over WiFi. The PLC logic is programmed to conditionally trigger events involving full-duplex transmission and processing of data between all nodes. The nodes in the integrated system are as follows:

| Node          | Function                             | Actual Host/Platform  |

|---------------|--------------------------------------|-----------------------|

| PLC           | Run EtherCAT MainDevice,             | Raspberry Pi 5B       |

|               | Modbus/TCP client, and control logic |                       |

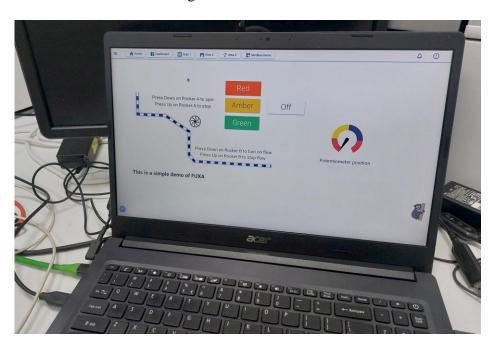

| HMI           | Host FUXA UI to visualize and        | Acer Aspire A315-57G  |

|               | read/write I/O data                  |                       |

| Remote        | Store fieldbus I/O history and       | Supabase on AWS       |

| Database      | commands from Mobile Client          | t4g.nano in Singapore |

| Mobile Client | Mobile HMI, send remote commands     | Samsung SM-A528B/DS   |

Table 4.2.5(c)-1: Nodes in Integrated System.

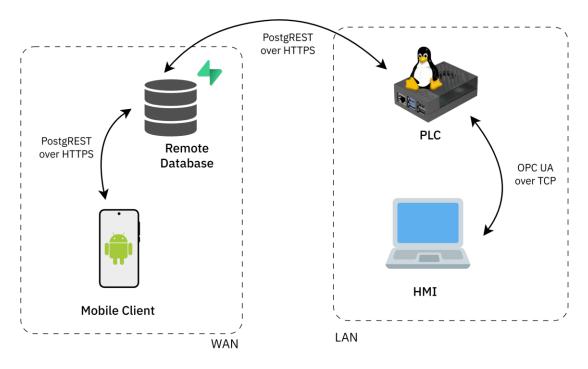

Figure 4.2.5(c)-1: Visualization of Nodes in the Integrated System.

In Figure 4.2.5(c)-1, "LAN" refers to the local TCP/IP network, which excludes the EtherCAT fieldbus, but not Modbus/TCP. However, data from Modbus/TCP is not directly accessed by nodes other than the PLC. The source of truth at the floor level is the OPC UA server, which the PLC hosts.

The integration test is fully qualitative. As the overall integrated system is not fully real-time (with the exception of the PLC logic and the EtherCAT fieldbus), temporal measurements were not measured as the WAN and LAN are inherently non-deterministic (all data transmitted over TCP, internet connection provided through WiFi, etc.), hence are unbounded. Latency between nodes in the integrated system also depends on the specific internet connection, service provider, time of day, etc. Therefore, no useful interpretation of temporal measurements can be made with respect to the integrated system.

# 4.2.5(d) Mock BAS Control Narrative

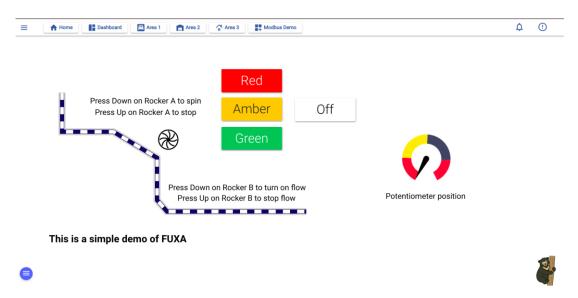

The mock BAS controls a fictional building composed of three arbitrary areas, presumably within 100m of each other. One can imagine them to be bedrooms, meeting rooms, garages, or a yard. Nevertheless, the effect of inputs on outputs are not limited based on the 'area' where the input device is located. The three arbitrary areas are served by three separate I/O devices: The E-bus terminals (EK1100 coupler cards); the K-bus terminals (BK1120 coupler cards), and the IRIV IO Controller. All fieldbus communication occurs over twisted pair Ethernet.

| Input   | Type                | Channels    | Area   | Active | Protocol |

|---------|---------------------|-------------|--------|--------|----------|

| Device  |                     |             | Served | Level  |          |

| KL1889  | Digital             | Channel 6   | 1      | LOW    | EtherCAT |

| KL6581  | Digital (or Analog, | Rocker A    | All    | -      |          |

| +KL6583 | data scheme is      | Rocker B    |        |        |          |

|         | arbitrary)          |             |        |        |          |

| EL1889  | Digital             | Channel 1-2 | 2      | LOW    |          |

| EL3024  | Analog, 4-20mA      | Channel 1   | 2      | -      |          |

| IRIV IO | Digital+Analog (0-  | AN0         | 3      | HIGH   | Modbus   |

|         | 10V or 4-20mA)      | DI0         |        |        | /TCP     |

Table 4.2.5(d)-1: Mock BAS fieldbus inputs.

The KL6581+KL6583 combo constitutes the EnOcean transceiver unit that receives digital data wirelessly from the batteryless PTM200 transmitter. Since the transceiver receives EnOcean datagrams and exposes the raw datagram in its process image, the form of the data (whether it is digital/analog) depends on the transmitter. In this case, the PTM200 is a simple digital switch.

| Output | Type    | Channels      | Area   | Active Level | Protocol |

|--------|---------|---------------|--------|--------------|----------|

| Device |         |               | Served |              |          |

| EL2889 | Digital | Channels 1-16 | 1      | LOW          | EtherCAT |

| KL2889 | Digital | Channels 1-16 | 2      |              |          |

Table 4.2.5(d)-2: Mock BAS fieldbus outputs.

| Transducer                | Type                     | Туре   |

|---------------------------|--------------------------|--------|

| PTM200                    | EnOcean Pushbutton       | Input  |

|                           | Transmitter Module       |        |

| Limit Switch              | Switch                   |        |

| Selector Switch           | Switch                   |        |

| E-stop Switch             | E-stop                   |        |

| Rotronic Hygroflex HF135- | Humidity and Temperature |        |

| SB1XDXXX                  | Sensor                   |        |

| Q-Light ST45B-3-24-RAG    | Tower Lights             | Output |

Table 4.2.5(d)-3: Mock BAS transducers.

Alarms and logs reside on the HMI/SCADA running on a separate computer. The PLC can also send notifications via a Telegram bot. There are two HMIs. The local HMI reads and writes tag values to/from the PLC via OPC UA over the LAN. The remote HMI is a mobile app reads and writes tag values to/from the PLC via a remote database. The remote HMI writes tag values using its 'Admiral' feature.

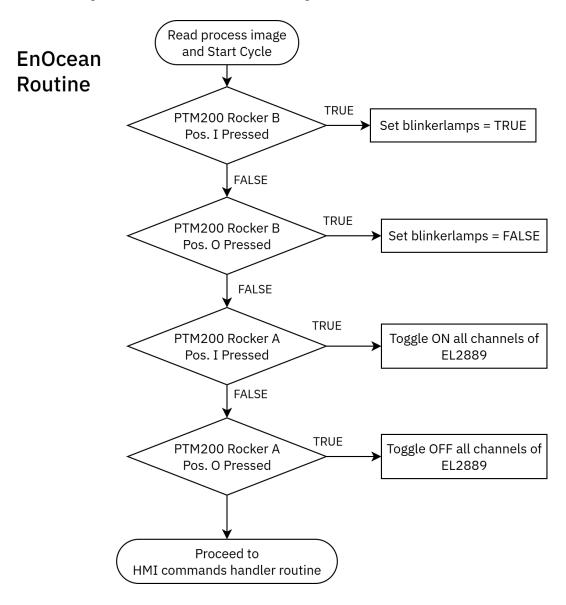

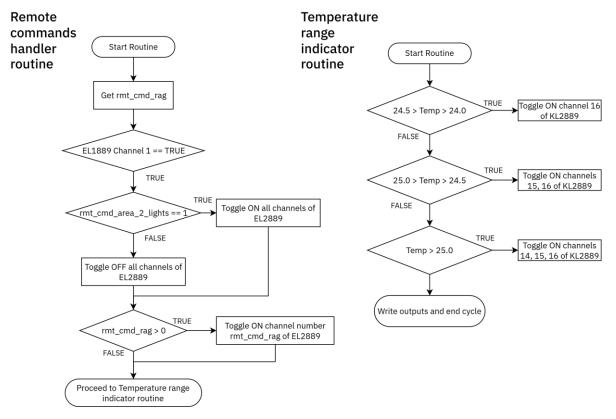

The following flow charts describe the PLC logic.

Figure 4.2.5(d)-1: EnOcean Routine in PLC program.

The control logic starts with the EnOcean routine, which handles inputs from the PTM200 and controls digital outputs and program flow via the blinkerlamps variable, which if TRUE, will blink all channels of the KL2889.

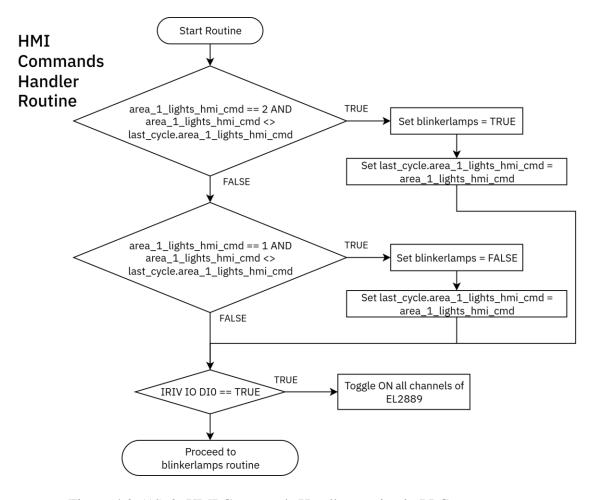

Figure 4.2.5(d)-2: HMI Commands Handler routine in PLC program.

The HMI may also control the same outputs controlled by the PTM200, however, priority is given to the PTM200 as its input may override that of the HMI.

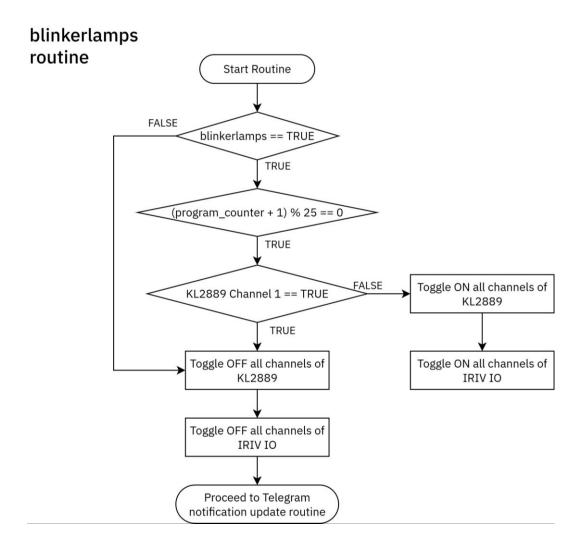

Figure 4.2.5(d)-3: Blinkerlamps routine in PLC program.

This routine only executes if the blinkerlamps variable is set, which occurs in the EnOcean routine and HMI Commands Handler routine as described in Figure 4.2.5(d)-1 and Figure 4.2.5(d)-2 respectively.

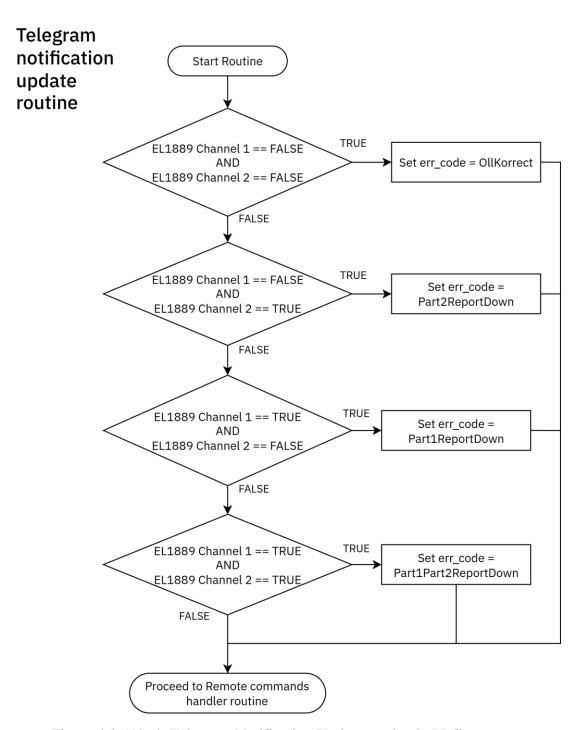

Figure 4.2.5(d)-4: Telegram Notification Update routine in PLC program.

The purpose of this routine is to demonstrate the Telegram bot. A direct message link to an appointed person in charge may be used to notify emergencies where urgent intervention is necessary.

Figure 4.2.5(d)-5: Remote Commands Handler routine in PLC program.

Figure 4.2.5(d)-6: Temperature Range Indicator routine in PLC program.

The Remote Commands Handler routine will only execute if Channel 1 of the EL1889 is toggled ON, functioning as an interlock. However in this case, since there is only a single action step conditioned on the 'interlock', it is effectively a simple permissive.

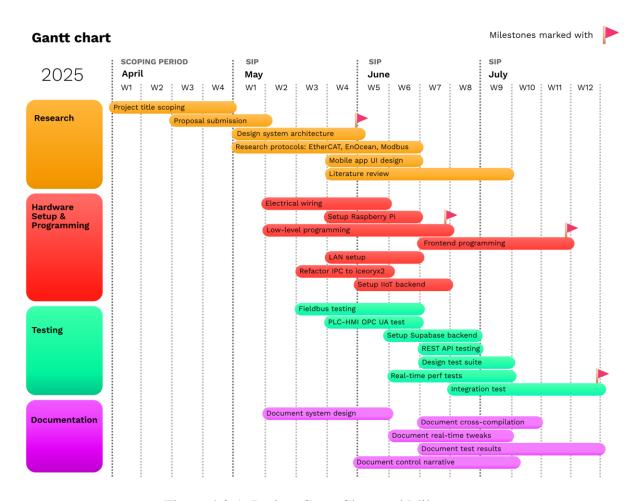

## **4.3 Gantt Chart and Milestones**

Figure 4.3-1: Project Gantt Chart and Milestones.

## **Milestones**

| Milestone                  | Completed in SIP Week |

|----------------------------|-----------------------|

| Design system architecture | 4                     |

| Low-level programming      | 7                     |

| Frontend programming       | 11                    |

| Integration test           | 12                    |

Table 4.3-1: Project Milestones and Week of Completion.

#### 5.0 Results and Discussion

Testing of the system focused predominantly on real-time performance, being that the core functionality implemented is an EtherCAT-based control loop. Despite targeting a building automation system as a mock application example, at the very minimum, the system should have reasonable soft real-time capability, backed up by empirical testing.

Integration testing for IIoT functionality was conducted without expectation of real-time behavior of the IIoT components, since there are no critical deadlines and arbitrary retries are allowed (a natural consequence of the TCP/IP stack). Much of the IIoT infrastructure was outsourced to cloud backend providers. Thus, testing involved simple verification of CRUD operations via the Supabase API. First using a REST testing tool to directly test the PostgREST API, as well as end user testing of the mobile app client.

#### 5.1 Results

The following tests were conducted without a GUI running, swap disabled, and wireless interfaces (Bluetooth and WiFi) soft blocked with *rfkill*. The Raspberry Pi 5 used was the basic B variant with 2GB of RAM. The Pi was not connected to the internet during real-time-performance-related testing. Also note that several non-real-time but critical processes are still run; namely, the OPC UA server and the Modbus/TCP polling process. The tx-usecs and rx-usecs parameters for the EtherCAT NIC were both set to 0 using *ethtool* to disable packet coalescing. In this analysis, 'jitter' refers to cycle activation jitter of the PLC, which is defined as the following:

$$Jitter = t_{sch,i-1} - t_{ins,i}$$

where i is the current cycle,  $t_{\text{sch},i-1}$  is the scheduled next cycle start time that was calculated in the immediate previous cycle, and  $t_{\text{ins},i}$  is the time instance calculated in the current cycle. The control loop thread is instructed to sleep until wakeup for the next cycle. Hence in using the definition above, jitter is always non-negative.

#### 5.1.1 *cyclictest* Latency Results

To establish baseline latency of the Pi 5, *cyclictest* was used, with additional stress loads run concurrently with *stress-ng*. This is conducted to survey the performance of the host hardware itself, generic with respect to the actual real-time application to be run.

| Run | Maximum per-        | Maximum per-thread         | Average of average per- |

|-----|---------------------|----------------------------|-------------------------|

|     | thread latency (µs) | latency average across all | thread latency (µs)     |

|     |                     | 8 threads (μs)             |                         |

| 1   | 148                 | 101.75                     | 15.75                   |

| 2   | 119                 | 104.00                     | 11.88                   |

| 3   | 128                 | 107.88                     | 12.38                   |

Table 5.1.1-1: Baseline Pi 5 latency results with stress load run concurrently.

#### 5.1.2 Worst-Case 48-Hour Soak Test

| Test results                | Release     |

|-----------------------------|-------------|

|                             | (1ms cycle) |

| Maximum jitter (μs)         | 210         |

| Maximum sleep interval (μs) | 121         |

Table 5.1.2-1: Maximum jitter and maximum sleep interval in µs over 48 hours.

A torture soak test was conducted over a span of 48 hours nonstop, with constant RAM utilization between 50-60%, and non-isolated CPU cores (CPU0-1) constantly utilized at 100%. The CPU temperature was verified to be below 60°C, far below the 85°C throttling threshold. *stress-ng* was used for the simulated CPU and RAM load, and was tweaked so that RAM utilization does not contend excessively and that the control loop remains operable.

### 5.1.3 12-Hour Soak Test

| Maximum jitter (μs)         | 206 |

|-----------------------------|-----|

| Maximum sleep interval (μs) | 220 |

Table 5.1.3-1: Maximum jitter and maximum sleep interval in μs over 12 hours.

(Release mode, 1ms cycle)

The 12-hour soak test recorded a similarly intolerable maximum jitter of  $206\mu s$ . While this is intolerable for <10ms cycles (jitter must be <200 $\mu s$ ), it is sufficient for slower cycles (>20ms) and is helpful in delineating where the real-time capability of the Pi 5 starts to fail. Similarly, the RAM utilization remained below the upper bound of 80%, staying between 50-60%.

## **5.1.4 Proxy Soak Test**

Short-term tests (10-20 minutes) recorded maximum jitters between 194-206 $\mu$ s. To simulate the 48-hour soak test maximum jitter, an additional 30% scaling was applied to the short-term test maximum jitter. This 30% rule-of-thumb scaling was derived from the ratio between the rounded highest and lowest recorded maximum jitters.

| Avg. RAM usage (%)          | 37    | 27    | 25    | 22    | 21    |

|-----------------------------|-------|-------|-------|-------|-------|

| Test results                |       |       |       |       |       |

| Scaled maximum jitter (µs)  | 188.5 | 160.0 | 160.0 | 100.1 | 154.7 |

| Maximum sleep interval (μs) | 7374  | 7558  | 7718  | 8241  | 7663  |

Table 5.1.4-1: Proxy soak tests with *stress-ng* RAM and CPU stress test running (**Debug** build mode, 10ms scan cycle).

| Avg. RAM usage (%) Test results | 34   | 27   | 24   | 20   | 20   |

|---------------------------------|------|------|------|------|------|

| Scaled maximum jitter (µs)      | 83.2 | 74.1 | 74.1 | 85.8 | 81.9 |

| Maximum sleep interval (μs)     | 133  | 147  | 147  | 239  | 126  |

Table 5.1.4-2: Proxy soak tests with *stress-ng* RAM and CPU stress test running (**Release** build mode, 500µs scan cycle).

The jitter upper limit is determined by the selected cycle period. The jitter must not exceed 2% of the cycle period. For a 10ms cycle, the maximum jitter must therefore be lower than  $200\mu s$ , and for a 5ms cycle, the maximum jitter must be lower than  $100\mu s$ .

## **5.1.5** Light Load Tests

Lighter load tests were conducted to see how light the system resource utilization has to be for the Pi to achieve better maximum jitter to support quicker scan cycles. This involved significantly reducing the amount of memory allocated to *stress-ng* memory stressor workers.

| Avg. RAM usage (%)          | 21   |

|-----------------------------|------|

| Scaled maximum jitter (µs)  | 27.3 |

| Maximum sleep interval (μs) | 8537 |

Table 5.1.5-1: Light load test results (**Debug** build mode, 10ms scan cycle).

| Avg. RAM usage (%)          | 18   |

|-----------------------------|------|

| Scaled maximum jitter (µs)  | 16.9 |

| Maximum sleep interval (μs) | 393  |

Table 5.1.5-2: Light load test results (**Release** build mode, 500µs scan cycle).

stress-ng was used to stress the memory using 64 concurrent workers, with 1MiB allocated to each. From this result, the achieved maximum jitter stayed bounded below 20-30μs. This is sufficient to support a 1ms scan cycle at the quickest (for a tolerance of <2% of cycle time maximum jitter). Depending on the exact application, the Pi is capable of fast motion control and multitasking, but is bottlenecked by the memory bus bandwidth.

From the results, the real-time performance of the Pi is not necessarily affected by the total percentage of RAM used, but rather the bandwidth utilization. The Pi is still capable of supporting scan cycles <10ms despite a large number of concurrent processes accessing RAM, but only such that each process does so in small enough chunks at one time.

## **5.1.6 Floating above Idle Test**

This test is run without *stress-ng* or any other stressors in the background, other than the components needed for operation. Real-time performance should always be tested with additional stress conditions. However, the results of this test show the asymptote of real-time performance as the system load tends towards idle (best performance under perfectly ideal low system load).

| Avg. RAM usage (%)          | 17   |

|-----------------------------|------|

| Scaled maximum jitter (µs)  | 19.5 |

| Maximum sleep interval (μs) | 8868 |

Table 5.1.6-1: Floating above idle test results (20-minute run, **Debug** build mode, 10ms scan cycle).

| Avg. RAM usage (%)          | 14   |

|-----------------------------|------|

| Scaled maximum jitter (µs)  | 14.3 |

| Maximum sleep interval (μs) | 405  |

Table 5.1.6-2: Floating above idle test results (20-minute run, **Release** build mode, 500µs scan cycle).

## 5.1.7 12-Hour Test: Floating above Idle

| Avg. RAM usage (%)          | 15  |

|-----------------------------|-----|

| Maximum jitter (μs)         | 22  |

| Maximum sleep interval (μs) | 289 |

Table 5.1.7-1: Floating above idle test results (12-hour run, **Release** build mode, 500µs scan cycle).

Without any stress load, the maximum jitter recorded over a 12-hour test run is 22µs. Comparing the 12-hour and the 20-minute run for the Release build, the 30% scaled maximum jitter is still significantly lower than the actual maximum jitter recorded. Hence, the 30% rule of thumb clearly does not work in this condition. Whilst the recorded maximum jitter is still lower than the 25µs upper bound (to satisfy <5% jitter for a 500µs cycle), it is not significantly lower with just a 3µs difference.

## 5.1.8 Testing of Heuristic: 12-Hour Light Soak Test

The additional 30% scaling heuristic was tested by conducting a 12-hour light soak test, using the same lighter stress load (upper bound of 25% RAM utilization).

| Avg. RAM usage (%)          | 22 |

|-----------------------------|----|

| Actual maximum jitter (μs)  | 78 |

| Maximum sleep interval (μs) | 78 |

Table 5.1.8-1: 12-hour light soak test results (Release build mode, 500µs scan cycle).

Given that in Table 5.1.4-2, the scaled maximum jitter was 74.1µs for the 24-27% RAM usage regime, it is not far off from the actual 78µs maximum jitter measured from the 12-hour run.

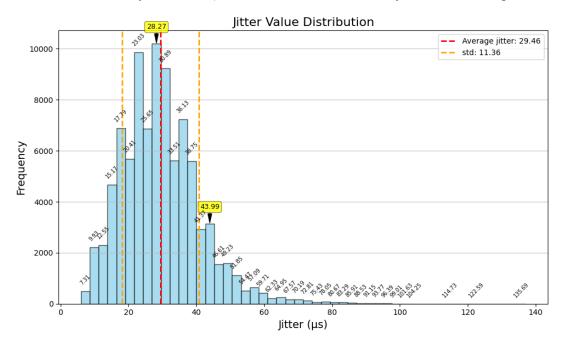

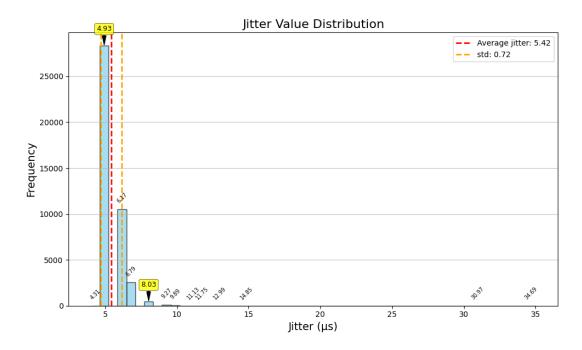

#### 5.1.9 Jitter Distribution

The following plots were obtained from short 20-minute test runs. Although real-time characteristics are quantified in terms of maximum jitter and latency recorded during worst-case scenarios, it is still useful to study the distribution of cycle jitter albeit from short test runs. In the following figures, the dashed orange lines indicate the boundary of  $\pm 10^{-1}$  (one standard deviation) away from the average.

Figure 5.1.9-1: Jitter Distribution under Stress Load.

Figure 5.1.9-2: Jitter Distribution when Floating above Idle.

In both Figure 5.1.9-1 and Figure 5.1.9-2, there is a long tail to the right that drops sharply from the average. In Figure 5.1.9-1, the distribution follows a more Bell-curve like shape, in contrast with Figure 5.1.9-2 that has more of an exponentially decreasing curve. Although the long right tail in Figure 5.1.9-1 also appears like an exponentially decreasing curve, more intermediate points exist between the average and the maximum values, whereas in Figure 5.1.9-2, the frequency drop is much more abrupt.

#### **5.1.10 Real-Time Performance Test Caveats**

There are some notable caveats with regards to the real-time performance of the Pi. Primarily, real-time performance may vary widely with respect to the software architecture. In this project, only one EtherCAT MainDevice is tested, which runs in user mode. Better real-time performance may be attainable using a kernel-mode EtherCAT MainDevice, such as the IgH Etherlab Master developed and maintained by Florian Pose (Ingenieurgemeinschaft, 2025). Despite these caveats, the test results indicate that the Pi is able to guarantee cycle times of at least 5ms with less than 2% maximum jitter for the majority of applications with sufficiently light system load.

## **5.1.11 IIoT Integration Test**

| Tested Aspect              | Qualitative Result                                |  |

|----------------------------|---------------------------------------------------|--|

| Supabase API Gateway Codes | All returned status code 200 (Success)            |  |

| PLC Real-Time Performance  | None. Cycle time fully respected and jitter stays |  |

| Impact                     | under 2% cycle time threshold (10ms cycle).       |  |

|                            | Maximum jitter recorded was 35μs.                 |  |

| Mobile Client              | Occasional UI rendering issues; Assets sometimes  |  |

|                            | load slowly and animations get skipped.           |  |

| HMI                        | UI elements respond slowly, but are sent to the   |  |

|                            | PLC relatively quickly.                           |  |

Table 5.1.11-2: Qualitative Integration Test Results.

Most issues uncovered during IIoT integration testing are frontend-related. Often having to do with the UI, this is not critical as the transmission of data on the backend of each node remains to be adequately reliable. One caveat of the integration test is that none of the nodes are subjected to soak tests, each node was subjected to normal loads, hence are not floating above idle, either.

Integration test durations are also short, as the internet connection is provided by the SM-A528B/DS hotspot. Using the building network to connect to the internet is a security risk, hence the duration of an integration test run never exceeded the duration of a work day.

#### 5.2 Discussion

If the Pi is used for deployment, it should be run in console mode only to reduce the overhead introduced by a graphical desktop environment. VNC, RDP, or any other remote GUI interfacing should be avoided, and disabled when the PLC is running its control loop(s). Any serious deployment of the Pi must also exclusively use a dedicated SSD for maximum reliability. A microSD card is simply not a reliable storage medium, especially for host hardware running real-time control software. Internet connection should best be limited to a dedicated non-real-time Ethernet NIC.

From experimentation, without the use of memory lock syscalls, GUI applications almost always cause some missed cycles. This might be due to disk I/O DMA, that cannot be preempted even by real-time tasks on SCHED\_FIFO. Calling mlockall() at the start of the real-time program seem to have made the real-time tasks resilient, even while the memory and disk I/O are stressed. As described in Madden (2019), the usage of memory locking in real-time contexts such as this is typical. Nevertheless, it is best for any graphical HMIs to be hosted on a separate device. The Pi is best suited for process data acquisition, light processing, and retransmission; to be done without the overhead of a graphical desktop environment.

With the knowledge that web browsers such as Chromium and Firefox require large memory and disk bandwidths, concurrent memory and disk stress tests were conducted using *stress-ng*, which reproduced the missed cycle deadlines and EtherCAT timeouts. Since this ultimately depends on hardware implementation of memory and disk I/O management of the host hardware, a different architecture (different SoC or a typical x86 motherboard configuration) may offer better real-time task resilience. However, mlockall() does provide a safeguard against page faults by guaranteeing that mapped pages of the calling process will stay in physical memory and are not evicted until munlockall() is called or the process terminates.

It is however, important to note that exact control operations of hardware resources cannot be preempted by user-space processes, despite being scheduled using SCHED\_FIFO at high priorities. Unbounded latencies may still occur due to hardware controller operations, which are outside the control of even the kernel.

Other possibly confounding factors namely inter-process communications were eliminated, both theoretically and experimentally. *iceoryx2* is a lock-free wrapper of shared memory for inter-process communications. As such, it could not have blocked on any RwLocks or Mutexes (as none exist in the API internal data path) and would have simply returned errors if samples are not successfully sent or received. This was also tested experimentally; with or without inter-process communication operations, the presence of missed deadlines only respond to significant concurrent memory and disk loads, which can be triggered by normal web browsing and *stress-ng*.

#### **5.2.1 Sub-Millisecond Real-Time Performance**

At least in Release build mode, the Pi is able to support sub-millisecond scan cycles, however, from testing, it is unable to support maximum cycle jitter of <3% of the cycle time for a 500µs cycle, if the specific PLC runtime architecture in this report is used without additional load (floating above idle). With a sufficiently light system load, it can achieve a maximum jitter of <5% of a 500µs cycle, amounting to a bound on the maximum jitter of 25µs. Since this level of performance is only observed with light stress tests, the ability to support sub-millisecond cycles on the Pi is only a limited guarantee and heavily depends on the exact application.

## **5.2.2** Comparison with Equivalent Benchmarks

Qiu, Varis, and McArthur (2024) tested a CODESYS system deployed on several Texas Instruments ARM SoCs. One SoC tested was the AM62x, a quad-core SoC with 512KB of shared L2 cache clocked at 1.4GHz maximum. The AM62x is the most equivalent SoC to the quad-core BCM2712 of the Raspberry Pi 5, though the BCM2712 does have a higher clock frequency at 2.4GHz.

The rest of the SoCs tested by Qiu et al. had specifications that were too disparate from the BCM2712 that would make it an unfair comparison either way. Namely, the AM69 is an octa-core SoC clocked at 2GHz with 1MB of shared L2 cache, while the AM64x is a dual-core SoC clocked at 800-1000MHz, with 256KB of shared L2 cache. It is important to note that the results from Qiu et al. did not involve a stress load running concurrently. Hence, an ideally light load.

| SoC    | Maximum jitter | Maximum cycle time | Minimum time spent |  |

|--------|----------------|--------------------|--------------------|--|

|        | recorded (µs)  | (µs)               | not working (μs)   |  |

| AM62x  | 116            | 700                | 300                |  |

| AM69   | 53             | 384                | 616                |  |

| TDA4VM | 65             | 371                | 629                |  |

| AM64x  | 973            | 1906               | 0                  |  |

Table 5.2.2-1: Adapted results from Qiu et al. (2024). The column "Minimum time spent not working" is derived by subtracting the 1ms cycle time used by Qiu et al. from the maximum recorded cycle time.